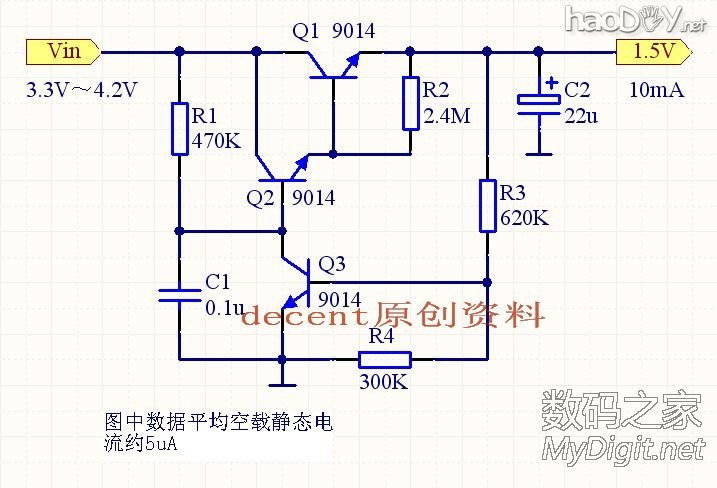

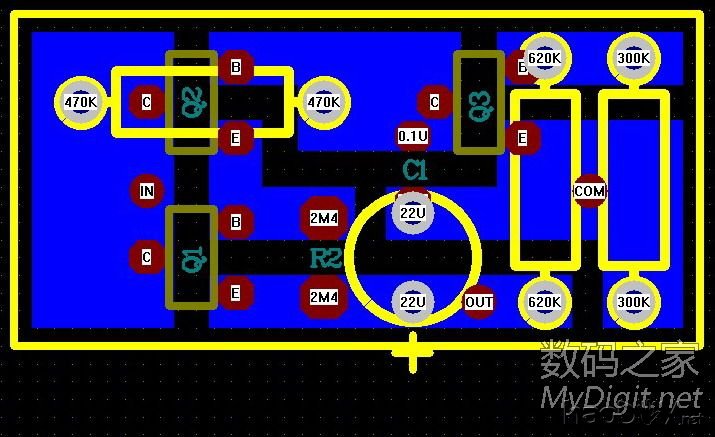

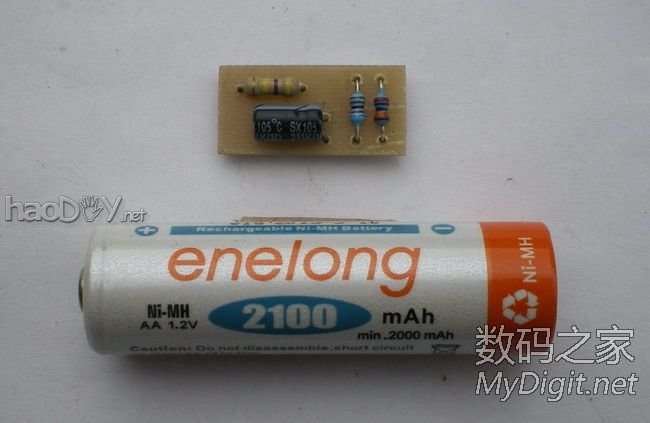

�����в��������Ӱ˵ľ�﮵磬������������ȴ��С ���ϲ���ʲô���棬ֻ�������ĸ�ȼ��������Ļ������ñ�ʲô�ġ� ���ϲ���ʲô���棬ֻ�������ĸ�ȼ��������Ļ������ñ�ʲô�ġ���������ֶ����˼����ʯӢ�ӣ��������һ����﮵罵��1.5V�����⡣���� ��ͨ������ѹ�����ĵ������������ʯӢ�ӹ��������������ֳ��겻���ͨ��������������Ӱ���ص�����ʱ�䡣 ��Ȼ���������ܽ�ѹ�ķ������Ա���������⣬����ֵ��ѹ�и����Ե�ȱ�㣬���������ѹ����������ѹͬ���仯��﮵�����磨4.2V�����յ磨3.3V����0.9V��ѹ�������������Զ��ʯӢ�����ܽ��ܵĵ�ѹ������Χ�����Ե���ص�ѹ����ʱ����ʹ���������û���꣬�����ѹ���Ѿ����в����ˡ� ����ܰ���ѹ��·������������Ľ������Ժ��Ե�ˮƽ����Ȼ����һ���Ƚ�����Ľ�������� ����û�к��ʵ���������IC����������һ����ʯӢ��ƽ������һ��ֻ����㼸mA���������������10mA�Ѵ´����࣬�����ڴˣ���������ѹ�������ĵ�����Ŀ�����5uA���ڣ� 1. ��·��������ͼ������ͨ�Ĵ�����ѹ���ζ�����ֻ����������ƶ����������ѹ����Ϊ�������������任��˼·�������˶���ѹ���ܵ��ѽ��������ĵ��������Ϊ��Ҫ���Ŀ�ꡣ ps�� ������һЩ���ѱ�ʾ���ÿ�����ѹ������������и��õĽ�ѹЧ�ʣ�������̸̸�ҵĿ����� ������ѹ����Ȼ�������Ը���ѹ��Ч�ʣ���ͬʱ�����ĵ����������Ҫ��Ŀǰ������1��2������������ͨӦ������������Ȼ���Ժ��ԣ����������ʹ��ʮuA����ĵ������Ҳ�Ǻ��ѽ��ܵġ� ����м��;�̬���ĵ�DCDCоƬ���ǿ��Կ��ǣ����Դ��������˵δ���ܸ㵽���Ƿ���������ʵ����Ҳ�Ͳ����ˡ�  2. ȫ�����ó�����Ԫ��������ҵ�����ƣ� R1����390K��560K��ȡֵԽС���������Ӧ���� R2��3M±20%���Ҿ��� R3��R4����ֵ���������ѹֵ��R3+R4����ֵ��1M±20%����Ϊ�ˣ�����ֵԽС�������Ҳ���������� C1����ͨ��Ƭ����Ƭ���ɣ�0.1u�Ǹ��ܳ����õĹ�� C2Ϊ4.7u��47u�����⣬����ѹҪ�� ������ֻҪ��С����NPN���ɣ������ͺţ�ֻϣ��β��������ò�����300�����ʵ�������ѣ�200����Ҳ���ԣ�ֻ����������������н��ͣ�����ʯӢ����˵����ʹ��5mAҲ�㹻�ˡ� 3. ����רΪ�ֹ����̰���Ƶ�PCB��ע����ͼ����ΪԪ���棩����·�ܼ��ö�����Ҳ������  4. �̺õİ��ӣ��ߴ�Լ21*10mm  5. ���Ӻõİ��ӣ���������Ϻ�����4����������������   (���α༭��admin)

(���α༭��admin) |

![[�������ó�Ʒ]DIY ATX��Դ��](/uploads/allimg/170709/1_0F9142633L54.jpg)